Synopsys Introduces Software-Defined Hardware-Assisted Verification to Enable AI Proliferation

Rhea-AI Summary

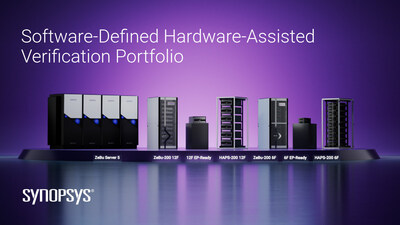

Synopsys (Nasdaq: SNPS) announced software-defined hardware-assisted verification (HAV) enhancements on March 11, 2026, delivering up to 2x performance and 2x capacity for ZeBu Server 5 and new HAPS-200 and ZeBu-200 12 FPGA platforms. New industry-first hardware-assisted test-automation and Real-Number Models enable earlier detection of cache-coherency and subsystem bugs and faster software bring-up across data center to edge AI designs. The HAPS-200 12 FPGA and HAPS-200 1 FPGA are available today; ZeBu-200 12 FPGA is available in Q3 2026. Continuous software updates and EP-Ready Hardware aim to extend system lifetime value and enable emulation-to-prototyping configurability.

Positive

- Up to 2x performance boost for ZeBu Server 5 via software-defined updates

- 2x capacity for HAPS-200 and ZeBu-200 12 FPGA platforms versus prior 6 FPGA systems

- Industry-first hardware-assisted test automation for earlier detection of cache-coherency and subsystem bugs

- HAPS-200 1 FPGA desktop platform available today for IP verification and software bring-up

- EP-Ready Hardware enables configurability between prototyping and emulation to extend reuse

Negative

- ZeBu-200 12 FPGA platform availability is scheduled for Q3 2026, creating staggered delivery across product line

News Market Reaction – SNPS

On the day this news was published, SNPS gained 0.08%, reflecting a mild positive market reaction.

Data tracked by StockTitan Argus on the day of publication.

Key Figures

Market Reality Check

Peers on Argus

SNPS was down 1.05% while key peers were mixed: NET +2.31%, PANW +0.06%, FTNT -0.10%, CRWD -1.95%, XYZ -0.61%, with no peers in the momentum scanner.

Previous AI Reports

| Date | Event | Sentiment | Move | Catalyst |

|---|---|---|---|---|

| Jan 06 | AI automotive showcase | Positive | +3.0% | Showcased AI-driven, software-defined automotive engineering efficiencies at CES 2026. |

| Oct 28 | AI & NVIDIA GTC | Positive | -1.8% | Highlighted Agentic AI and GPU-accelerated simulation at NVIDIA GTC Washington, D.C. |

| Oct 08 | AI simulation adoption | Positive | +2.4% | Showcased Ansys SimAI platform usage for >10x faster automotive simulations. |

| Sep 03 | EDA AI expansion | Positive | +0.0% | Expanded Synopsys.ai Copilot capabilities, boosting design speed and engineer productivity. |

| Jul 29 | Ansys AI release | Positive | +7.3% | Ansys 2025 R2 introduced broad AI-powered simulation enhancements and tools. |

Recent AI-tagged news for SNPS has typically led to modest positive moves, with four of five events showing gains and one negative outlier despite positive AI messaging.

Over the past year, SNPS has issued multiple AI-focused updates spanning automotive engineering, GPU-accelerated simulation, and AI-enabled design workflows. AI-tagged events on Jul 29, 2025, Sep 3, 2025, Oct 8, 2025, Oct 28, 2025, and Jan 6, 2026 highlighted faster simulations, productivity gains, and deeper NVIDIA collaborations. Price reactions were mostly positive, suggesting investors often reward clear AI productivity benefits. Today’s HAV announcement fits this ongoing AI-enablement trajectory in verification and system design.

Historical Comparison

Across five recent AI-tagged announcements, SNPS saw an average move of 2.17%, mostly positive. The new HAV AI verification update continues this pattern of emphasizing AI-driven productivity and scale.

AI-tag history shows a progression from AI-enhanced simulation and design tools toward broader, system-level and automotive applications, now extending into large-scale hardware-assisted verification for complex AI silicon.

Market Pulse Summary

This announcement detailed new software-defined, hardware-assisted verification platforms delivering up to 2x performance and capacity and targeting quadrillions of verification cycles for advanced AI silicon. In context of prior AI-tagged updates that boosted simulation speed and engineering productivity, it extends Synopsys’ AI story deeper into verification. Investors may watch adoption of the HAPS-200 and ZeBu-200 systems, delivery timelines into Q3 2026, and how these capabilities support complex data center and edge AI workloads.

Key Terms

hardware-assisted verification technical

fpga technical

emulation technical

prototyping technical

cache‑coherency technical

real-number models (rnm) technical

fault emulation technical

ip verification technical

AI-generated analysis. Not financial advice.

New product capabilities deliver leading performance, capacity, and industry-first hardware-assisted test-automation capabilities to accelerate AI silicon innovation from data center to edge

Key Highlights

- Software-defined approach enables an up to 2x performance boost for ZeBu Server 5 and scales capacity up to 2x with modular HAV for AI-era mega designs

- New HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms for mainstream designs feature EP‑Ready Hardware that extends emulation and prototyping capacity by 2x and delivers leading performance for emulation and prototyping use cases

- New, industry-first hardware-assisted test automation capabilities enable faster, earlier detection of cache‑coherency and subsystem‑level bugs for maximum coverage

AI chip verification complexity is escalating rapidly as large language models continue to double in size roughly every four months, and interface data rates advance at a 2x rate every three years. Simultaneously, edge AI architectures are driving aggressive throughput, latency, and power‑efficiency targets that further expand the design and validation workload. To keep pace, the industry requires HAV solutions to support broader application coverage and run quadrillions of verification cycles, enabling first‑time‑right silicon and a seamless ability to integrate heterogeneous AI systems.

"As AI-driven systems become more complex, verification must scale just as quickly. Hardware-assisted verification is no longer optional. It is critical to meeting aggressive time-to-market goals and ensuring silicon readiness," said Salil Raje, Senior Vice President and General Manager, Adaptive and Embedded Computing Group, AMD. "FPGA-based emulation and prototyping play a central role in that effort by accelerating system bring-up and enabling earlier software development. Our collaboration with Synopsys reflects that focus. Through joint optimization of Synopsys ZeBu with the AMD Vivado™ software stack, and by leveraging AMD EPYC™ processors for compute acceleration, we are reducing compile times and helping customers move to accurate system models faster."

"As AI becomes more pervasive across almost every industry and products are now workload-optimized and silicon-powered, building high confidence early that the workloads are running to spec on the silicon under development is critical," said Ravi Subramanian, Chief Product Management Officer at Synopsys. "Our software-defined, hardware-assisted verification solutions deliver continuous innovation. They are a powerful force multiplier to scale verification productivity and meet the growing demand for pre-silicon development across industries."

The latest advancements across Synopsys' software-defined hardware-assisted verification portfolio, include:

Breakthrough performance and capacity for the AI era: The latest software-defined updates and modular HAV are available across the ZeBu and HAPS platforms. Of note, with these updates, the industry's highest capacity-scalable emulation platform, ZeBu Server 5, supports complex designs to meet the demands of mega designs supporting data center AI training and inference, GPU, custom accelerators, and networking IPU/DPU workloads. Modular HAV for HAPS enables the largest prototypes for software development, with further improvements for compute, storage, and bring-up capabilities.

New HAPS and ZeBu platforms: The new HAPS-200 12 FPGA and ZeBu-200 12 FPGA systems address the complexity and high-performance requirements for data center-sub-system, mobile, client, server, consumer, and edge AI applications. They deliver 2x higher capacity compared to previous 6 FPGA platforms utilizing the flagship AMD Versal™ Premium VP1902 adaptive SoCs, offering EP-Ready Hardware-enabled configurability between prototyping and emulation. Synopsys also introduces the new HAPS-200 1 FPGA platform as a desktop system ideal for IP verification and software bring-up using Synopsys Interface Prototyping Kits.

"As NVIDIA's AI platforms have become software‑defined to meet rising performance and scalability demands, verification must evolve in the same way," said Narendra Konda, Vice President, Hardware Engineering at NVIDIA. "Synopsys' software‑defined hardware‑assisted verification and the new HAPS‑200 12 FPGA systems are accelerating our system‑level verification and validation, helping us deliver complex AI platforms on aggressive schedules. And, Synopsys modular hardware-assisted verification enables deeper collaboration across our ecosystem."

Software-defined HAV capabilities extend system lifetime value: Continuous software improvements deliver compounding performance gains, increased debug productivity, as well as additional use case capabilities for both new and installed systems. The Synopsys HAV portfolio supports new, industry-first Hardware-Assisted Test Solutions, test automation capabilities that allow teams to stress corner cases for processor, memory, and I/O subsystems as well as full-system coherency validation and observe system behavior under realistic workloads in emulation long before silicon is ready. For mixed-signal and system-level designs, Real-Number Models (RNM) emulation enables fast, scalable abstraction of analog behavior within digital-centric verification flows for faster software bring-up. For safety-critical and high-reliability designs, new fault emulation capabilities enable scalable fault injection and analysis across RTL simulation, emulation, and prototyping.

"Verifying hardware for our highly anticipated rack-scale AMD Helios solution – marked by massive AI scale, complex subsystems, and robust software stacks – demands scalable and versatile verification platforms," said Alex Starr, Corporate Fellow, AMD. "The Synopsys software-defined, HAV capabilities with EP-Ready Hardware are critical to how we perform CPU, GPU, and AI subsystems verification as well as full-system validation. Teams can also cover an expanded number of use cases in the pre-silicon phase, encompassing analog, digital, and software design verification using Real-Number Models (RNM) in emulation. As well, the flexibility to reconfigure and reuse hardware across projects and move seamlessly between emulation and prototyping as AI designs grow in both physical size and software stack volume are essential to delivering the high-performance, interoperable AI infrastructure at scale needed to meet the world's growing AI demands."

Availability & Additional Resources

Software-defined enhancements are being rolled out continuously across the HAV portfolio, with the new capabilities available to users today. The new EP‑Ready HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms are available today and in Q3 2026, respectively. HAPS-200 1 FPGA platform is available today.

- Product Page: Synopsys HAV Solutions Family

- Blog: Introducing Software-Defined Hardware-Assisted Verification: A New Benchmark for AI-Era Chip Design

- Video: Software-Defined Hardware-Assisted Verification for the AI Era

Follow Synopsys Converge 2026 News and Updates

Synopsys Converge is taking place March 11-12, 2026, at the

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the leader in engineering solutions from silicon to systems, enabling customers to rapidly innovate AI-powered products. We deliver industry-leading silicon design, IP, simulation and analysis solutions, and design services. We partner closely with our customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at www.synopsys.com.

© 2026 Synopsys, Inc. All rights reserved. Synopsys, Ansys, the Synopsys and Ansys logos, and other Synopsys trademarks are available at https://www.synopsys.com/company/legal/trademarks-brands.html. AMD EPYC, Versal, Vivado and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other company or product names may be trademarks of their respective owners.

Contacts

Media

Kelli Wheeler: kelliw@synopsys.com

Pete Smith: pete.smith@synopsys.com

corp-pr@synopsys.com

![]() View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

SOURCE Synopsys, Inc.